# 32-Bit Proprietary Microcontroller

**CMOS**

# FR60 MB91350A Series

# MB91F355A/MB91355A/MB91354A/MB91V350A

#### ■ DESCRIPTION

The FR families are lines of standard single-chip microcontrollers each based on a 32-bit high-performance RISC CPU, incorporating a variety of I/O resources and bus control features for embedded control applications which require high CPU performance for

This FR60 family is based on FR30 and FR40 families and enhanced is bus access. The FR60 family is a line of single-chip oriented microcontrollers incorporating a wealth of peripheral resources.

The FR60 family is optimized for embedded control applications requiring high processing power of the CPU, such as DVD player, navigation, high performance Fax machine, and printer controls.

#### **■ FEATURES**

#### 1. FR CPU

- 32-bit RISC, load/store architecture with a five-stage pipeline

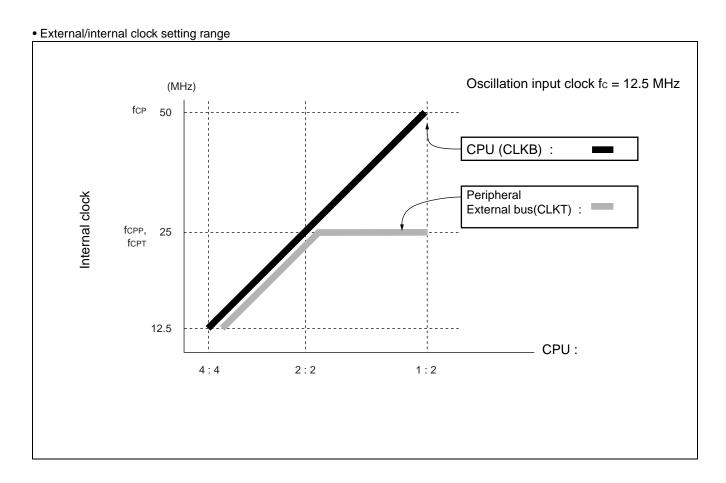

- Maximum operating frequency: 50 MHz (using the PLL at an oscillation frequency of 12.5 MHz)

- 16-bit fixed length instructions (basic instructions), 1 instruction per cycle

- Instruction set optimized for embedded applications: Memory-to-memory transfer, bit manipulation, barrel shift etc.

- Instructions adapted for high-level languages: Function entry/exit instructions, multiple-register load/store instructions

(Continued)

## ■ PACKAGE

I2C license

Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use, these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- · Register interlock functions: Facilitating coding in assemblers

- On-chip multiplier supported at the instruction level.

Signed 32-bit multiplication: 5 cycles. Signed 16-bit multiplication: 3 cycles

- Interrupt (PC, PS save): 6 cycles, 16 priority levels

- · Harvard architecture allowing program access and data access to be executed simultaneously

- FR family instruction compatible

#### 2. Bus Interface

- Maximum operating frequency: 25 MHz

- Capable of up to 24-bit address full output (16 MB of space)

- 8,16-bit data output

- Built-in pre-fetch buffer

- Non-used data and address pin are usable as general I/O port.

- Capable of chip-select signal output for completely independent four areas settable in 64 KB minimum

- Support for various memory interfaces:

SRAM, ROM/FLASH,

page mode FLASH ROM, page mode ROM

- Basic bus cycle: 2 cycles

- Programmable automatic wait cycle generator capable of inserting wait cycles for each area

- RDY input for external wait cycles

- Support for fly-by transfer for DMA, which enables wait control of independent I/O

### 3. Mounted Memory

| Memory           | MB91V350A | MB91F355A | MB91355A | MB91354A |

|------------------|-----------|-----------|----------|----------|

| ROM              | No        | 512 KB    | 512 KB   | 384 KB   |

| RAM (stack)      | 16 KB     | 16 KB     | 16 KB    | 8 KB     |

| RAM (executable) | 16 KB     | 8 KB      | 8 KB     | 8 KB     |

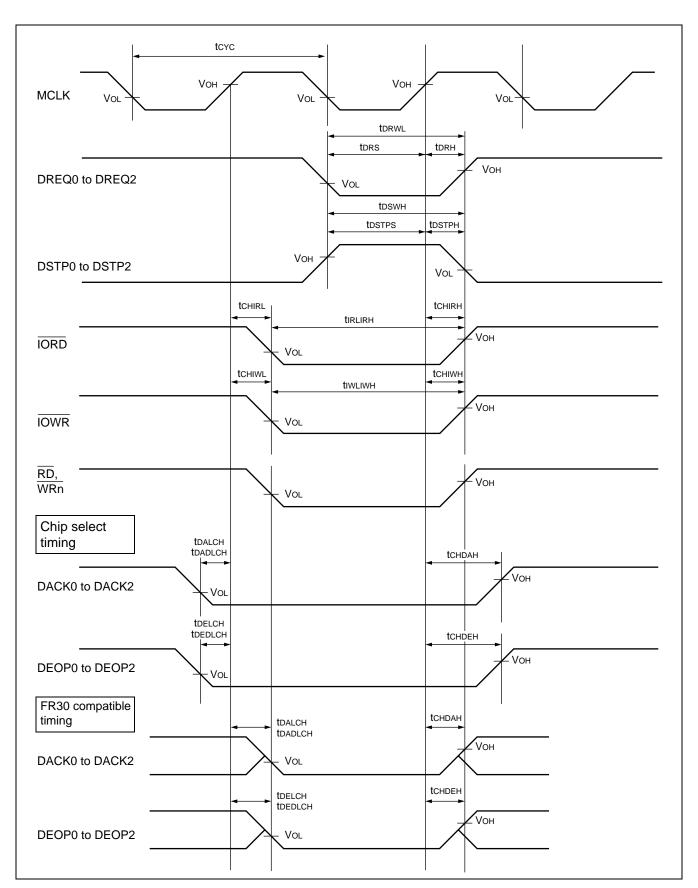

## 4. DMAC (DMA Controller)

- Capable of simultaneous operation of up to 5 channels (3 channels for external → external operation)

- Three transfer sources (external pin, internal peripheral, software) selectable by software. (Transfer can be started from UART0/1/2.)

- Addressing using 32-bit full addressing mode (increment, decrement, fixed)

- Transfer modes (demand transfer, burst transfer, step transfer, block transfer)

- Support for fly-by transfer (between external I/O and memory)

- Selectable transfer data size: 8, 16, or 32-bit

- Multi-byte transfer enabled (by software)

- DMAC descriptor in IO areas (200<sub>H</sub> to 240<sub>H</sub>, 1000<sub>H</sub> to 1024<sub>H</sub>)

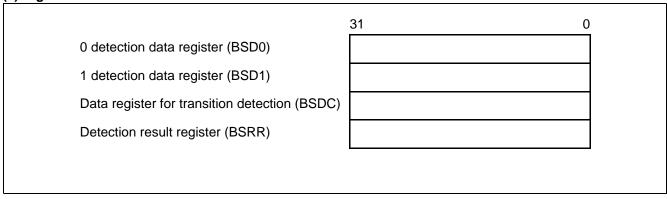

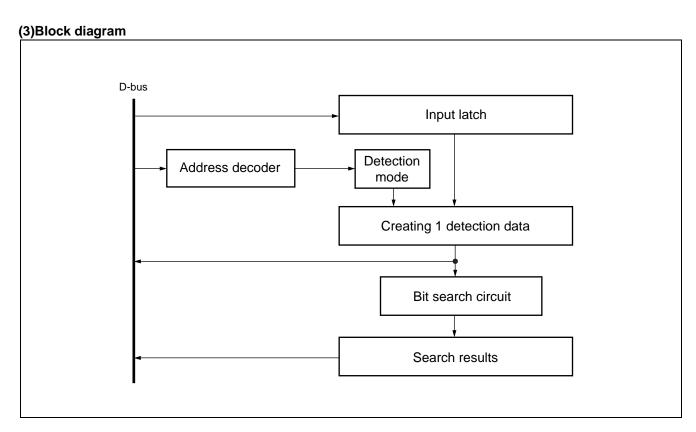

## 5. Bit Search Module (for REALOS)

• Search for the position of the bit 1/0-changed first in 1 word from the MSB

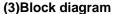

#### 6. Various Timers

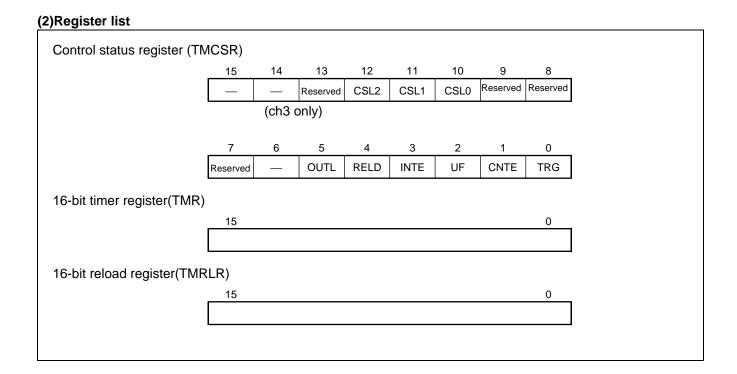

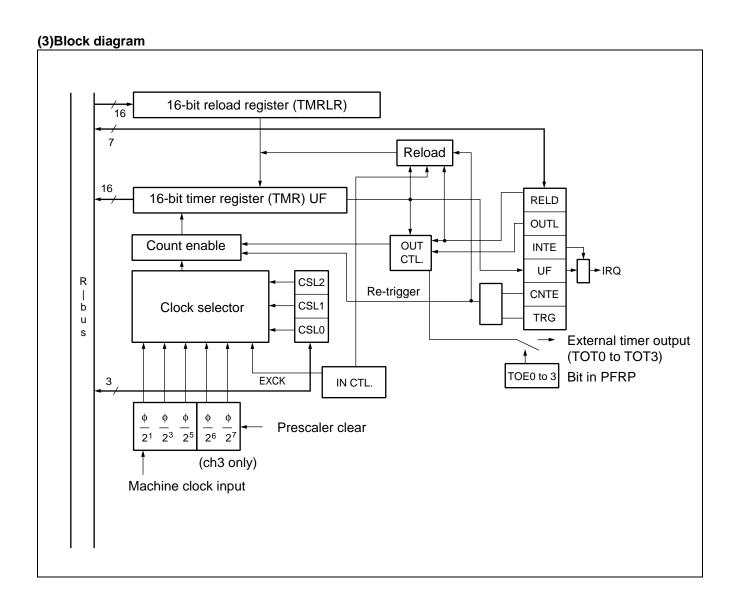

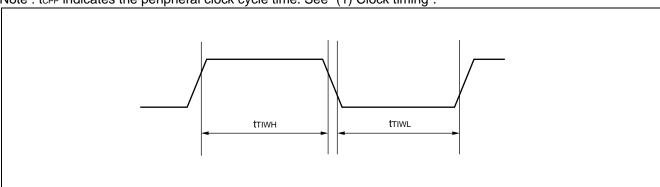

• 4 channels of 16-bit reload timer (including 1 channel for REALOS):

Internal clock frequency selectable from among divisions by 2/8/32 (division by 64/128 selectable only for ch3)

• 16-bit free-running timer: 1 channel.

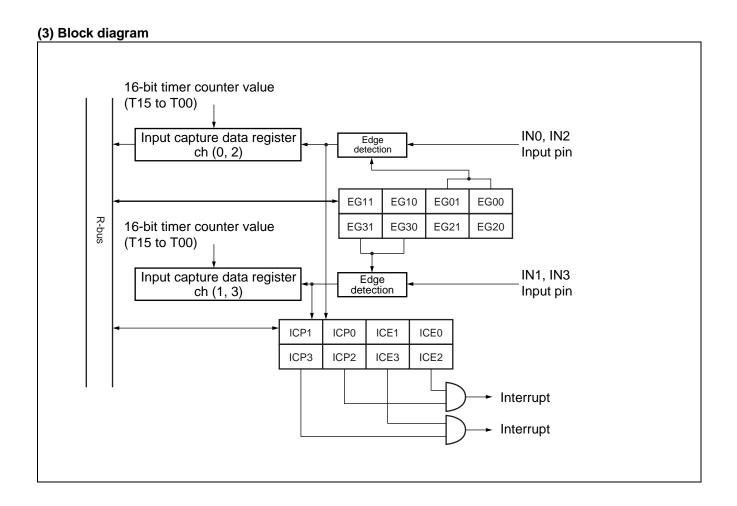

Output compare module: 8 channels. Input capture module: 4 channels

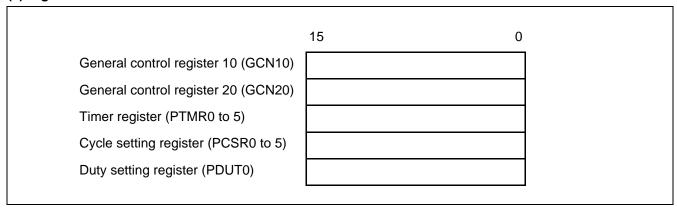

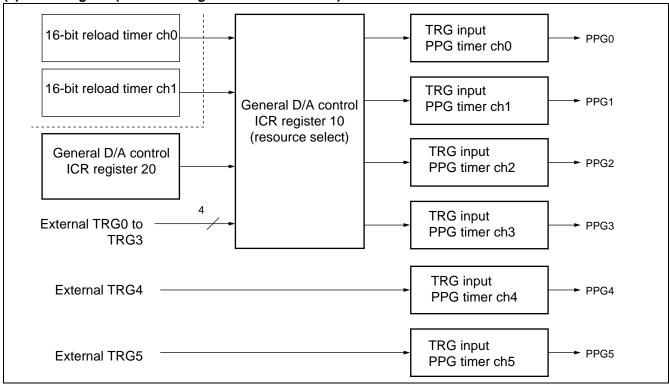

• 16-bit PPG timer 6 channels

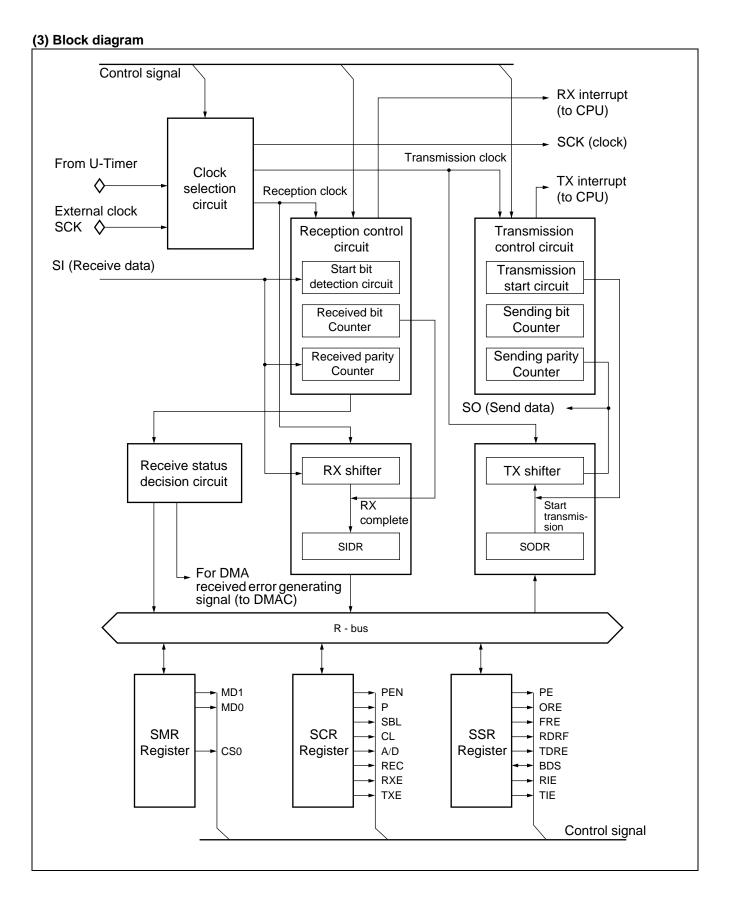

#### 7. UART

- UART Full duplex double buffer 5 channel

- Selectable parity On/Off

- Asynchronous (start-stop synchronized) or CLK-synchronous communications selectable

#### (Continued)

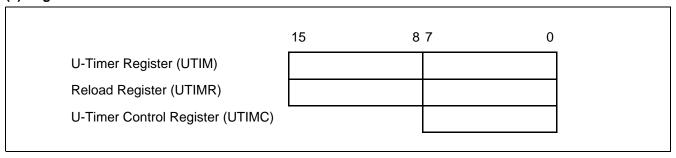

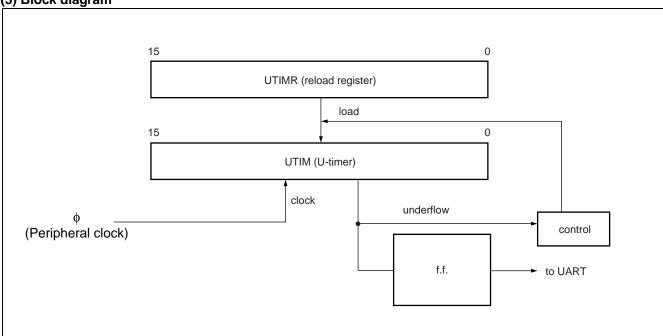

- Internal timer for dedicated baud rate

- External clock can be used as transfer clock

- Assorted error detection functions (for parity, frame, and overrun errors)

- 115 Kbps support

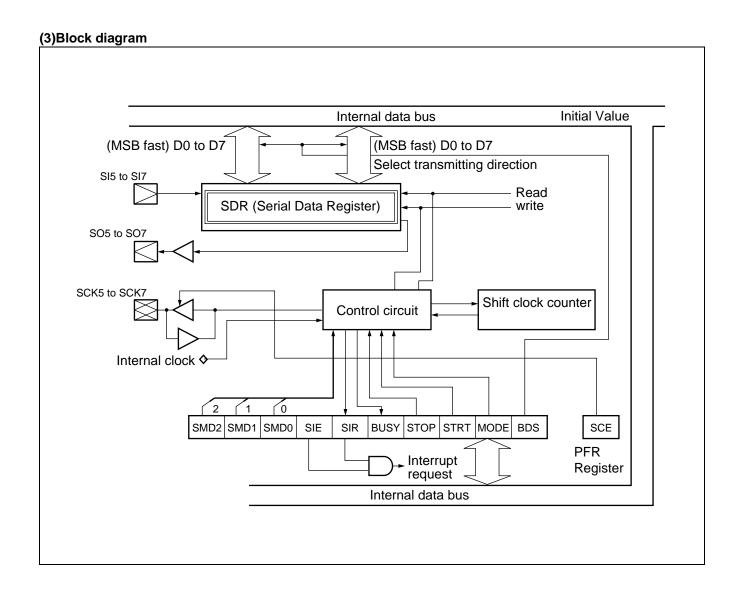

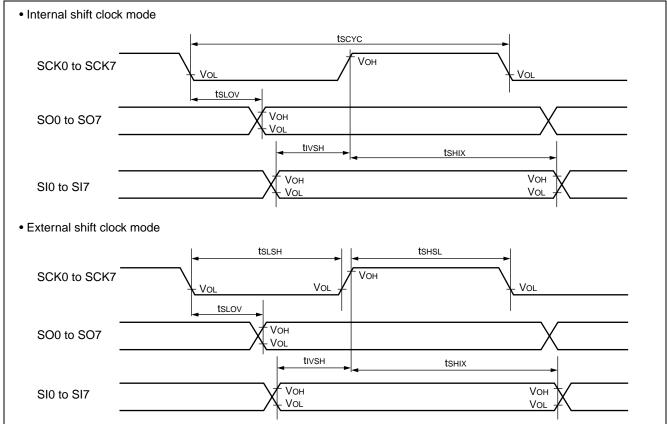

#### 8. SIO

- 3 channels for 8-bit data serial transfer

- · Shift clock selectable from among internal three and external one

- Shift direction selectable (transfer from LSB or MSB) selectable

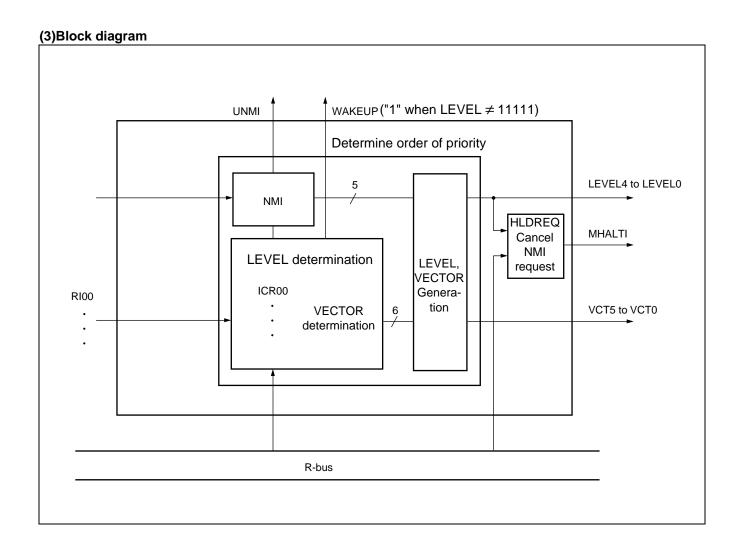

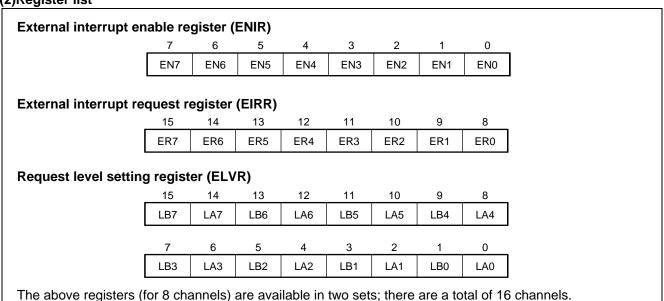

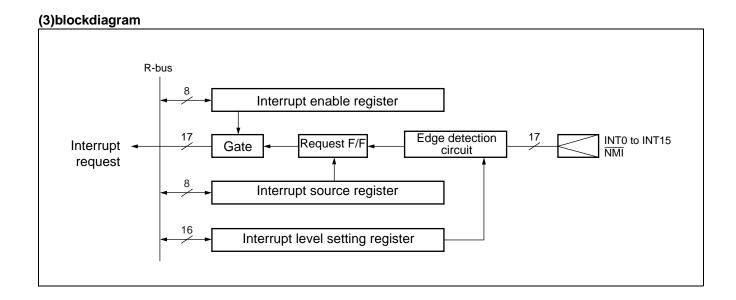

### 9. Interrupt Controller

- Total of 17 external interrupt lines (1 nonmaskable interrupt pin and 16 normal interrupt pins available for Wake Up from STOP)

- interrupt from internal peripheral

- Programmable priorities (16 levels) for all interrupts except the non-maskable interrupt

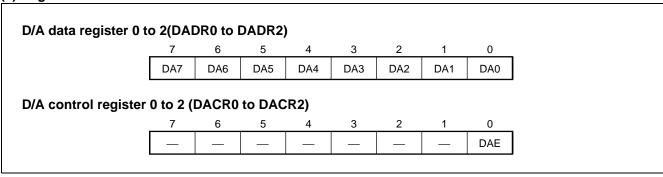

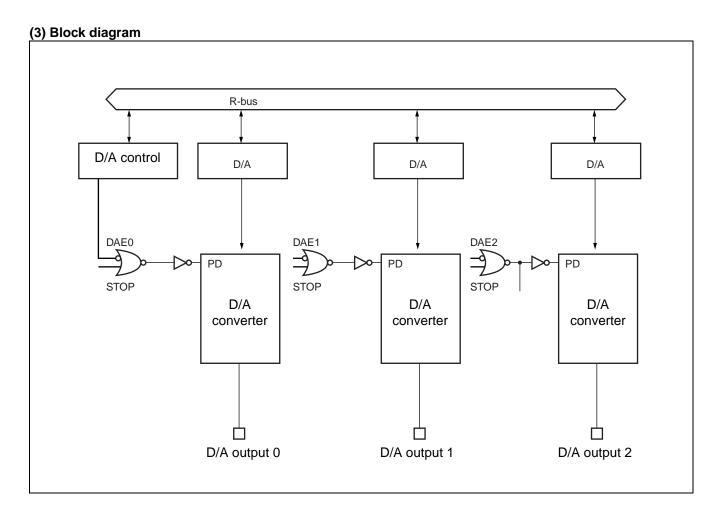

#### 10. D/A Converter

• 8-bit resolution, 3 channels

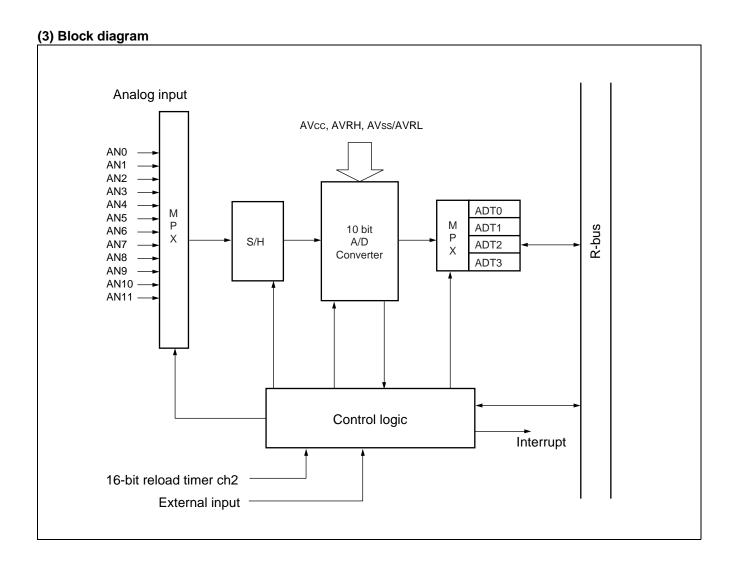

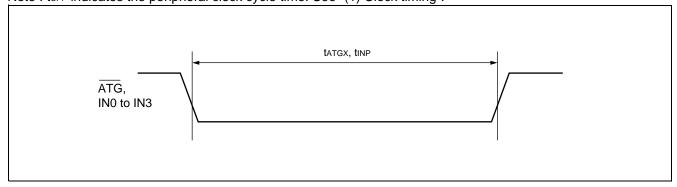

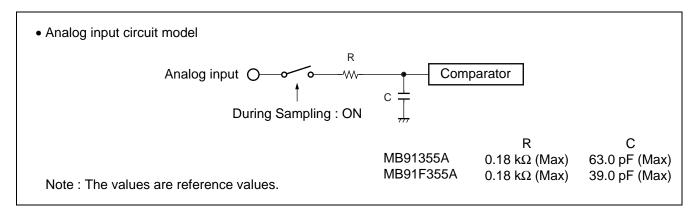

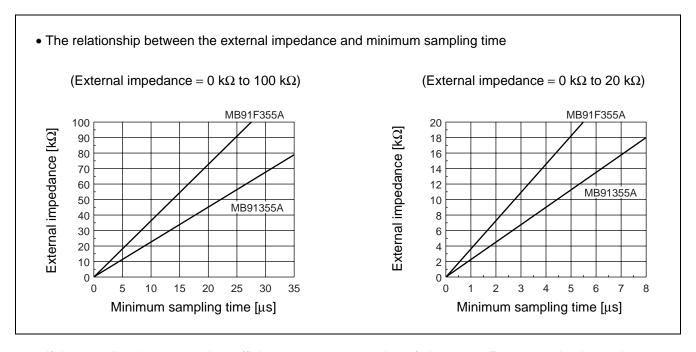

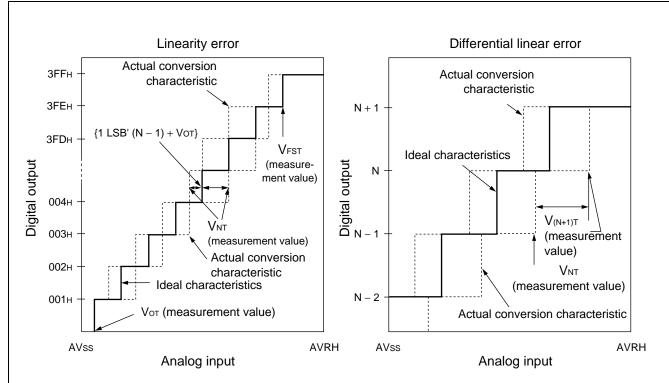

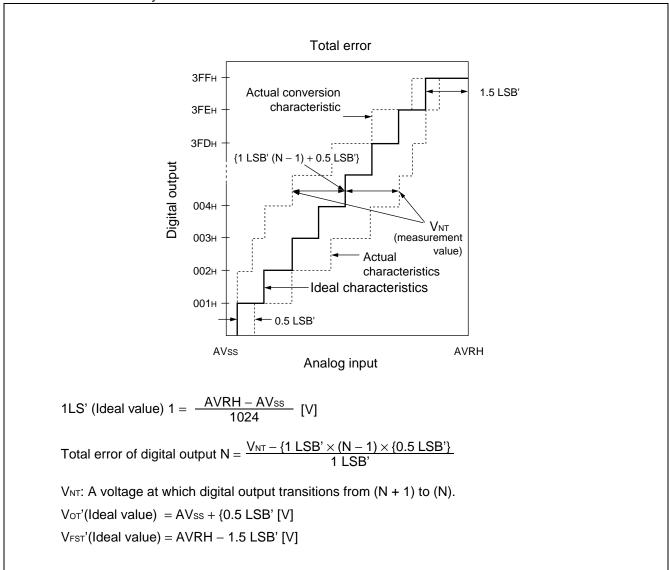

#### 11. A/D Converter

- 10-bit resolution. 12 channels

- Casting time for serial/parallel conversion: 1.48 μs

- Conversion mode (single conversion mode, continuous conversion mode)

- Activation source (software, external trigger, peripheral interrupt)

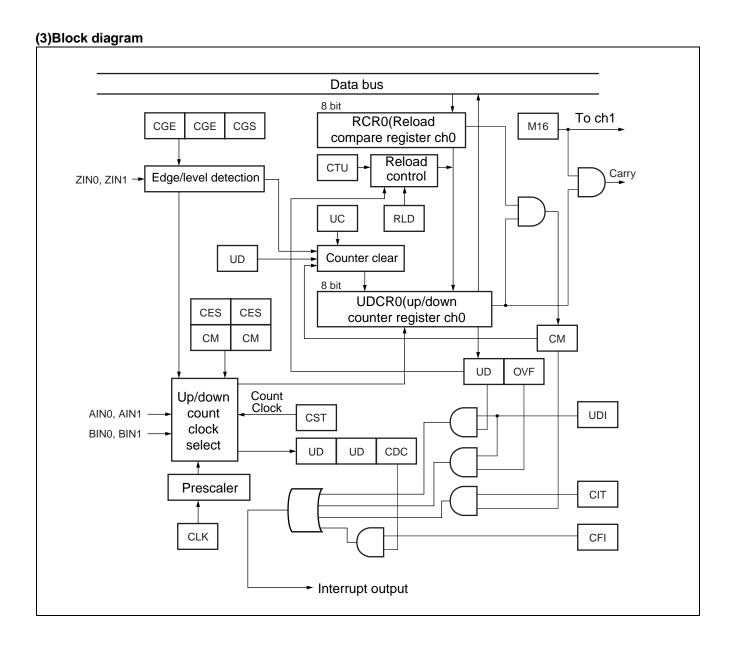

#### 12. Other Interval Timer/Counter

- 8/16-bit up/down counter

- 16-bit PPG timer 5 channels

- Watch dog timer

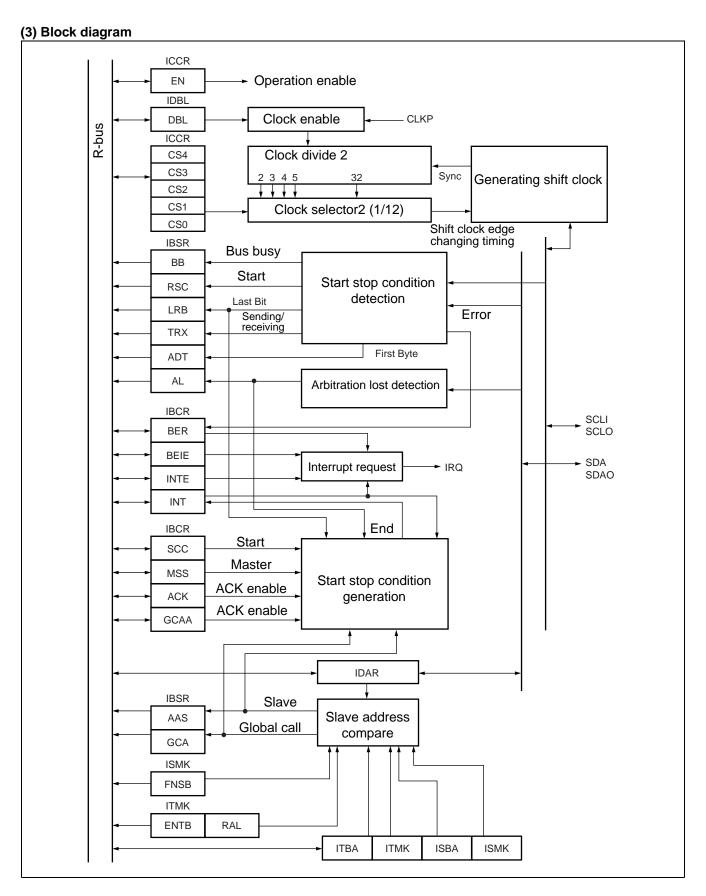

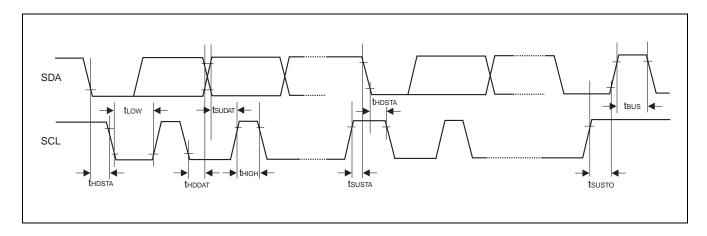

### 13. I<sup>2</sup>C Bus Interface (400 Kbps supported)

- 1channel master/slave sending and receiving

- Arbitration and clock synchronization

### 14. I/O Port

- 3 V I/O ports (16 ports shared for external interrupts support 5 V input.)

- Max 126 ports

#### 15. Other Features

- Internal oscillator circuit as clock source, allowing PLL multiplication to be selected

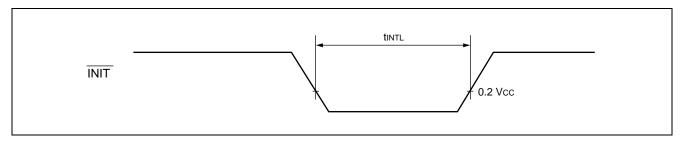

- Provided with INIT as a reset pin (The CPU operates without oscillation stabilization wait interval when the INIT pin is reset.)

- others, watch-dog timer reset, software reset enable

- Support for stop and sleep modes for low power consumption, capable of saving power during CPU operation at 32 kHz.

- Gear function

- Built-in time base timer

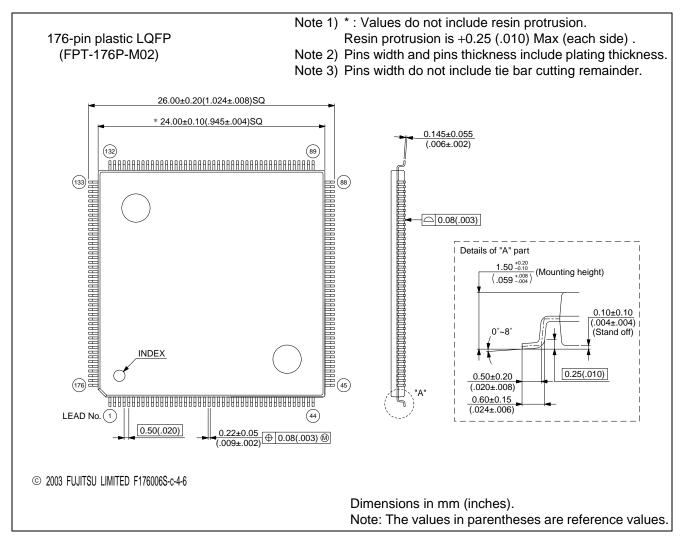

- Package: LQFP-176 (lead pitch: 0.50 mm)

- CMOS technology(0.35 μm)

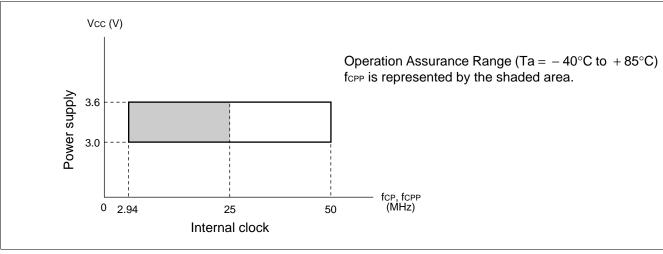

- Power supply voltage: 3.3 V ± 0.3 V

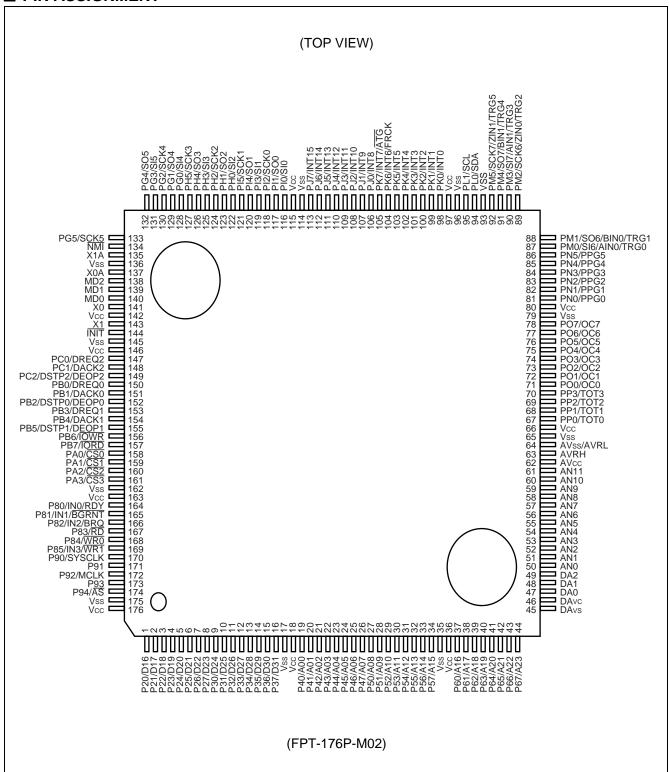

### **■ PIN ASSIGNMENT**

# ■ PIN DESCRIPTION

| Pin no.  | Pin name     | Circuit type | Description                                                                                             |  |

|----------|--------------|--------------|---------------------------------------------------------------------------------------------------------|--|

| 1 to 8   | D16 to D23   | С            | External data bus bit 16 to bit 23. Enabled in external bus mode.                                       |  |

| 1 10 6   | P20 to P27   | C            | Available as a port in external bus 8-bit mode.                                                         |  |

| 9 to 16  | D24 to D31   | С            | external data bus bit 24 to bit 31. Enabled in external bus mode.                                       |  |

| 91010    | P30 to P37   |              | Usable as port at single chip mode.                                                                     |  |

| 19 to 26 | A00 to A07   | С            | Bits 0 to 7 of external address bus. Enabled in external bus mode.                                      |  |

| 19 10 26 | P40 to P47   |              | Usable as port at single chip mode.                                                                     |  |

| 27 to 34 | A08 to A15   | С            | Bits 8 to 15 of external address bus. Enabled in external bus mode.                                     |  |

| 27 10 34 | P50 to P57   | C            | Usable as port at single chip mode.                                                                     |  |

|          | A16 to A20   |              | Bits 16 to 20 of external address bus. Enabled in external bus mode.                                    |  |

| 37 to 41 | P60 to P64   | С            | Available as a port either in single chip mode or with no external address bus in use.                  |  |

|          | A21 to A23   |              | Bits 21 to 23 of external address bus. Enabled in external bus mode.                                    |  |

| 42 to 44 | P65 to P67   | С            | Available as a port either in single chip mode or with no external address bus in use.                  |  |

| 47 to 48 | DA0, DA1     |              | D/A converter output pin.                                                                               |  |

| 49       | DA2          |              | D/A converter output pin.                                                                               |  |

| 50 to 57 | AN0 to AN7   | G            | Analog input pin.                                                                                       |  |

| 58 to 61 | AN8 to AN11  | G            | Analog input pin.                                                                                       |  |

|          | TOT0 to TOT3 |              | Reload timer output port. This function is enabled when timer output is enabled.                        |  |

| 67 to 70 | PP0 to PP3   | D            | General purpose input/output port. This function is enabled when the timer output function is disabled. |  |

|          | OC0          |              | Output compare pin.                                                                                     |  |

| 71       | PO0          | D            | General purpose I/O. This function is available as a port when the output compare output is not in use. |  |

|          | OC1          |              | Output compare pin.                                                                                     |  |

| 72       | PO1 D        |              | General purpose I/O. This function is available as a port when the output compare output is not in use. |  |

|          | OC2          |              | Output compare pin.                                                                                     |  |

| 73       | PO2          | D            | General purpose I/O. This function is available as a port when the output compare output is not in use. |  |

|          | OC3 to OC7   |              | Output compare pin.                                                                                     |  |

| 74 to 78 | IDU3 to DU2  |              | General purpose I/O. This function is available as a port when the output compare output is not in use. |  |

|          | PPG0         |              | PPG timer output pin.                                                                                   |  |

| 81       | PN0          | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.      |  |

| Pin no. | Pin name | Circuit type | Description                                                                                                                                                               |  |

|---------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | PPG1     |              | PPG timer output pin.                                                                                                                                                     |  |

| 82      | PN1      | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.                                                                        |  |

|         | PPG2     |              | PPG timer output pin.                                                                                                                                                     |  |

| 83      | PN2      | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.                                                                        |  |

|         | PPG3     |              | PPG timer output pin.                                                                                                                                                     |  |

| 84      | PN3      | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.                                                                        |  |

|         | PPG4     |              | PPG timer output pin.                                                                                                                                                     |  |

| 85      | PN4      | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.                                                                        |  |

|         | PPG5     |              | PPG timer output pin.                                                                                                                                                     |  |

| 86      | PN5      | D            | General purpose I/O. This function is available as a port when the PPG timer output is not in use.                                                                        |  |

|         | SI6      | D            | Data input for serial I/O6. Since this input is used as required when serial I/O 6 is in input operation, the port output must remain off unless intentionally turned on. |  |

| 87      | AIN0     |              | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                        |  |

| 07      | TRG0     |              | External trigger input for PPG timer0. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                 |  |

|         | PM0      |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                               |  |

|         | SO6      |              | Data output for serial I/O 6. This function is enabled when the serial I/O6 data output is enabled.                                                                       |  |

| 88      | BIN0     | D            | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                        |  |

| 00      | TRG1     |              | External trigger input for PPG timer1. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                 |  |

|         | PM1      |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                               |  |

|         | SCK6     |              | Clock input/output for serial I/O 6. This function is enabled when serial I/O6 is using the external shift clock mode, or serial I/O5 clock output function is enabled.   |  |

| 89      | ZIN0     | D            | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                        |  |

| 09      | TRG2     |              | External trigger input for PPG timer2. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                 |  |

|         | PM2      |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                               |  |

| Pin no.   | Pin name        | Circuit type | Description                                                                                                                                                                                                                              |

|-----------|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | SI7             |              | Data input for serial I/O 7. Since this input is used as required when serial I/O 7 is in input operation, the port output must remain off unless intentionally turned on.                                                               |

| 90        | AIN1            | D            | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                                       |

|           | TRG3            |              | External trigger input for PPG timer 3. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                               |

|           | PM3             |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                                                                                              |

|           | SO7             |              | Data output for serial I/O 7. This function is enabled when the serial I/O 7 data output is enabled.                                                                                                                                     |

| 91        | BIN1            | 6            | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                                       |

| 91        | TRG4            | D            | External trigger input for PPG timer 4. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                               |

|           | PM4             |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                                                                                              |

|           | SCK7            | . D          | Clock input/output for serial I/O5. This function is enabled when serial I/O 7 is using the external shift clock mode, or serial I/O 5 clock output function is enabled.                                                                 |

| 00        | ZIN1            |              | 8/16-bit up/down counter input. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                                       |

| 92        | TRG5            |              | External trigger input for PPG timer 5. Since this input is used as required when enabled, the port output must remain off unless intentionally turned on.                                                                               |

|           | PM5             |              | General purpose I/O. This function is available a port when the serial I/O, 8/16-bit up/down counter, and PPG timer outputs are not in use.                                                                                              |

| 94        | SDA             | F            | Clock input/output pin for I <sup>2</sup> C bus. This function is enabled when the I <sup>2</sup> C system is enabled for operation in standard mode. The port output must remain off unless intentionally turned on. (Open drain input) |

|           | PL0             |              | General purpose input/output port. This function is available as a port when the I <sup>2</sup> C system is disabled for operation. (Open drain input)                                                                                   |

| 95        | SCL             | F            | Clock input/output pin for I <sup>2</sup> C bus. This function is enabled when the I <sup>2</sup> C system is enabled for operation in standard mode. The port output must remain off unless intentionally turned on. (Open drain input) |

|           | PL1             |              | General purpose input/output port. This function is available as a port when the I <sup>2</sup> C system is disabled for operation. (Open drain input)                                                                                   |

| 98 to 103 | INT0 to<br>INT5 | E            | External interrupt input. Since this input is used as required when the corresponding external interrupt is enabled, the port output must remain off unless intentionally turned on.                                                     |

|           | PK0 to PK5      |              | General purpose input/output port.                                                                                                                                                                                                       |

| Pin no.       | Pin name         | Circuit type | Description                                                                                                                                                                                                            |  |

|---------------|------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 104           | INT6             |              | External interrupt input. Since this input is used as required when the corresponding external interrupt is enabled, the port output must remain off unless intentionally turned on.                                   |  |

|               | FRCK             | E            | External clock input pin for freerun timer. Since this input is used as required when selected as the external clock input for the free running timer, the port output must remain off unless intentionally turned on. |  |

|               | PK6              |              | General purpose input/output port.                                                                                                                                                                                     |  |

|               | INT7             |              | External interrupt input. Since this input is used as required when the corresponding external interrupt is enabled, the port output must remain off unless intentionally turned on.                                   |  |

| 105           | ĀTG              | E            | External trigger input for A/D converter. Since this input is used as required when selected as an A/D activation source, the port output must remain off unless intentionally turned on.                              |  |

|               | PK7              |              | General purpose input/output port.                                                                                                                                                                                     |  |

| 106 to<br>113 | INT8 to<br>INT15 | E            | External interrupt input. Since this input is used as required when the corresponding external interrupt is enabled, the port output must remain off unless intentionally turned on.                                   |  |

|               | PJ0 to PJ7       |              | General purpose input/output port.                                                                                                                                                                                     |  |

| 116           | SI0              | D            | UART0 data input. Since this input is used as required when UART0 is in input operation, the port output must remain off unless intentionally turned on.                                                               |  |

|               | PI0              |              | General purpose input/output port.                                                                                                                                                                                     |  |

| 117           | S00              | D            | UART0 data output. This function is enabled when the UART0 data output is enabled.                                                                                                                                     |  |

| 117           | PI1              |              | General purpose input/output port. This function is enabled when the data output function of UART0 is disabled.                                                                                                        |  |

| 118           | SCK0             | D            | UART0 clock input/output pin. This function is enabled either when clock output enabled or when UART0 inputs the external clock signal.                                                                                |  |

| 110           | Pl2              |              | General purpose input/output port. This function is enabled when UART0 is not using the external clock signal with the UART0 clock output function disabled.                                                           |  |

| 119           | SI1              | D            | UART1 data input. Since this input is used as required when UART1 is in input operation, the port output must remain off unless intentionally turned on.                                                               |  |

|               | PI3              |              | General purpose input/output port.                                                                                                                                                                                     |  |

| 120           | SO1              | D            | UART1 data outpu. This function is enabled when the UART1 data output is enabled.                                                                                                                                      |  |

| 120           | PI4              |              | General purpose input/output port. This function is enabled when the data output function of UART1 is disabled.                                                                                                        |  |

| 101           | SCK1             | D            | UART1 clock input/output pin. This function is enabled either when clock output enabled or when UART1 inputs the external clock signal.                                                                                |  |

| 121           | PI5              |              | General purpose input/output port. This function is enabled when UART1 is not using the external clock signal with the UART1 clock output function disabled.                                                           |  |

| Pin no. | Pin name | Circuit type | Description                                                                                                                                                              |                                                                                                             |

|---------|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 122     | SI2      | D            | UART2 data input. Since this input is used as required when UART2 is in input operation, the port output must remain off unless intentionally turned on.                 |                                                                                                             |

|         | PH0      |              | General purpose input/output port.                                                                                                                                       |                                                                                                             |

| 123     | SO2      |              | UART2 data outpu. This function is enabled when the UART2 data output is enabled.                                                                                        |                                                                                                             |

| 123     | PH1      | D            | General purpose input/output port. This function is enabled when the data output function of UART2 is disabled.                                                          |                                                                                                             |

| 124     | SCK2     | D            | UART2 clock input/output pin. This function is enabled either when the UART2 clock output is enabled or when UART2 inputs the external clock signal.                     |                                                                                                             |

| 124     | PH2      |              | General purpose input/output port. This function is enabled when UART2 is not using the external clock signal with the UART2 clock output function disabled.             |                                                                                                             |

| 125     | SI3      | D            | UART3 data input. Since this input is used as required when UART3 is in input operation, the port output must remain off unless intentionally turned on.                 |                                                                                                             |

|         | PH3      |              | General purpose input/output port.                                                                                                                                       |                                                                                                             |

| 126     | SO3      | _            | UART3 data outpu. This function is enabled when the UART3 data output is enabled.                                                                                        |                                                                                                             |

| 120     | 126 PH4  | D            | General purpose input/output port. This function is enabled when the data output function of UART3 is disabled.                                                          |                                                                                                             |

| 127     | SCK3     |              | UART0 clock input/output pin. This function is enabled either when the UART3 clock output is enabled or when UART3 inputs the external clock signal.                     |                                                                                                             |

| 127     | PH5      | D            | General purpose input/output port. This function is enabled when UART3 is not using the external clock signal with the UART3 clock output function disabled.             |                                                                                                             |

| 128     | SI4      | D            | UART4 data input. Since this input is used as required when UART4 is in input operation, the port output must remain off unless intentionally turned on.                 |                                                                                                             |

|         | PG0      |              | General purpose input/output port.                                                                                                                                       |                                                                                                             |

| 129     | SO4      | D            | UART4 data output. This function is enabled when the UART4 data output is enabled.                                                                                       |                                                                                                             |

| 129     | PG1      |              | General purpose input/output port. This function is enabled when the data output function of UART4 is disabled.                                                          |                                                                                                             |

| 120     | SCK4     | _            | UART4 clock input/output pin. This function is enabled either when the UART4 clock output is enabled or when UART4 inputs the external clock signal.                     |                                                                                                             |

| 130     | PG2      | D            | General purpose input/output port. This function is enabled when UART4 is not using the external clock signal with the UART4 clock output function disabled.             |                                                                                                             |

| 131     | SI5      | D            | Data input for serial I/O5. Since this input is used as required when serial I/O5 is in input operation, the port output must remain off unless intentionally turned on. |                                                                                                             |

|         | PG3      |              | General purpose input/output port.                                                                                                                                       |                                                                                                             |

| 122     | SO5      | D            | Data output for serial I/O5. This function is enabled when the serial I/O5 data output is enabled.                                                                       |                                                                                                             |

| 132     | PG4      | PG4          | D                                                                                                                                                                        | General purpose input/output port. This function is enabled when the I/O5 data output function is disabled. |

| Pin no.       | Pin name      | Circuit type | Description                                                                                                                                                                                                                |  |

|---------------|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 133           | SCK5          |              | Clock innput/output for serial I/O5. This function is enabled when serial I/O5 is using the external shift clock mode, or serial I/O5 clock output function is enabled.                                                    |  |

| 155           | PG5           | D            | General purpose input/output port. This function is enabled when serial I/O5 is not using the external shift clock mode with the serial I/O5 clock output function disabled.                                               |  |

| 134           | NMI           | Н            | NMI (Non Maskable Interrupt) input                                                                                                                                                                                         |  |

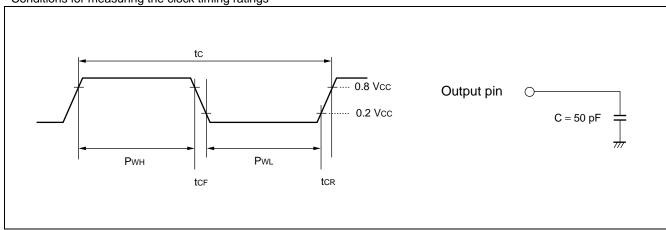

| 135           | X1A           | В            | Output clock cycle time. Sub clock                                                                                                                                                                                         |  |

| 137           | X0A           | В            | Input clock cycle time. Sub clock                                                                                                                                                                                          |  |

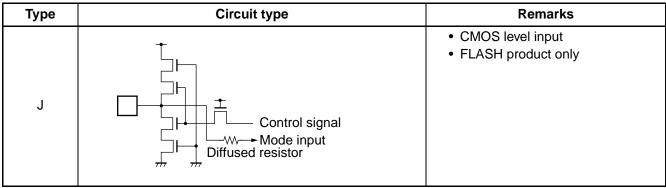

| 138 to<br>140 | MD2 to<br>MD0 | H, J         | 2 to 0Mode Pins. The levels applied to these pins set the basic operating mode.  Connect VCC or VSS.  Input circuit configuration:  The production model (masked-ROM model) is type "H".  The FLASH ROM model is type "J". |  |

| 141           | X0            | А            | Input clock cycle time. Main clock                                                                                                                                                                                         |  |

| 143           | X1            | Α            | Output clock cycle time. Main clock                                                                                                                                                                                        |  |

| 144           | ĪNIT          | I            | External reset input                                                                                                                                                                                                       |  |

| 147           | DREQ2         | С            | External input for DMA transfer requests. Since this input is used as required when selected as a DMA start source, the port output must remain off unless intentionally turned on.                                        |  |

|               | PC0           |              | General purpose input/output port.                                                                                                                                                                                         |  |

| 148           | DACK2         | С            | External acknowledge output for DMA transfer requests. This function is enabled when the transfer request acceptance output for DMA is enabled.                                                                            |  |

| 140           | PC1           |              | General purpose input/output port. This function is enabled when the transfer request acceptance output for DMA is enabled.                                                                                                |  |

|               | DEOP2         |              | Completion output for DMA external transfer. This function is enabled when the external transfer end output for DMA is enabled.                                                                                            |  |

| 149           | DSTP2         | С            | Stop input for DMA external transfer. This function is enabled when the external transfer stop input for DMA is enabled.                                                                                                   |  |

|               | PC2           |              | General purpose input/output port. This function is enabled when the external transfer end output and external transfer stop input for DMA are disabled.                                                                   |  |

| 150           | DREQ0         | С            | External input for DMA transfer requests. Since this input is used as required when selected as a DMA start source, the port output must remain off unless intentionally turned on.                                        |  |

|               | PB0           |              | General purpose input/output port.                                                                                                                                                                                         |  |

| 151           | DACK0         | С            | External acknowledge output for DMA transfer requests. This function is enabled when the transfer request acceptance output for DMA is enabled.                                                                            |  |

| 151           |               |              | General purpose input/output port. This function is enabled when the transfer request acceptance output for DMA is disabled.                                                                                               |  |

| Pin no. | Pin name | Circuit type | Description                                                                                                                                                                         |  |

|---------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | DEOP0    |              | Completion output for DMA external transfer. This function is enabled when the external transfer end output for DMA is enabled.                                                     |  |

| 152     | DSTP0    | С            | Stop input for DMA external transfer. This function is enabled when the external transfer stop input for DMA is enabled.                                                            |  |

|         | PB2      |              | General purpose input/output port. This function is enabled when the external transfer end output and external transfer stop input for DMA are disabled.                            |  |

| 153     | DREQ1    | С            | External input for DMA transfer requests. Since this input is used as required when selected as a DMA start source, the port output must remain off unless intentionally turned on. |  |

|         | PB3      |              | General purpose input/output port.                                                                                                                                                  |  |

| 154     | DACK1    |              | External acknowledge output for DMA transfer requests. This function is enabled when the transfer request acceptance output for DMA is enabled.                                     |  |

| 154     | PB4      | С            | General purpose input/output port. This function is enabled when the external transfer request acceptance output for DMA is disabled.                                               |  |

|         | DEOP1    | С            | Completion output for DMA external transfer. This function is enabled when the external transfer end output for DMA is enabled.                                                     |  |

| 155 DS  | DSTP1    |              | Stop input for DMA external transfer. This function is enabled when the external transfer stop input for DMA is enabled.                                                            |  |

|         | PB5      |              | General purpose input/output port. This function is enabled when the external transfer end output and external transfer stop input for DMA are disabled.                            |  |

| 156     | IOWR     | С            | Write strobe output for DMA fly-by transfer. This function is enabled when the DMA fly-by transfer write strobe output is enabled.                                                  |  |

| 156     | PB6      |              | General purpose input/output port. This function is enabled when the DMA fly-by transfer write strobe output is disabled.                                                           |  |

| 157     | ĪORD     | С            | Read storobe output for DMA fly-by transfer. This function is enabled when the DMA fly-by transfer read strobe output is enabled.                                                   |  |

| 157     | PB7      |              | General purpose input/output port. This function is enabled when the DMA fly-by transfer read strobe output is disabled.                                                            |  |

| 150     | CS0      | С            | Chip select 0 output. Enable at external bus mode                                                                                                                                   |  |

| 158     | PA0      |              | General purpose input/output port. This is enabled at single chip mode.                                                                                                             |  |

| 159     | CS1      | С            | Chip select 1 output. This function is enabled when the chip select 1 output is enabled.                                                                                            |  |

| เอษ     | PA1      |              | General purpose input/output port. This function is enabled when the chip select 1 output is disabled.                                                                              |  |

| 160     | CS2      | C            | Chip select 2 output. This function is enabled when the chip select 2 output is enabled.                                                                                            |  |

| 160     | PA2      |              | General purpose input/output port. This function is enabled when the chip select 2 output is disabled.                                                                              |  |

| Pin no. | Pin name | Circuit type | Description                                                                                                                                                                          |  |

|---------|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 161     | CS3      | С            | Chip select 3 output. This function is enabled when the chip select 3 output is enabled.                                                                                             |  |

| 101     | PA3      | O            | General purpose input/output port. This function is enabled when the chip select 3 output is disabled.                                                                               |  |

|         | RDY      |              | External ready input. The pin has this function when external ready input is enabled.                                                                                                |  |

| 164     | IN0      | D            | Input capture input pin. Since this input is used as required when selected as an input capture input, the port output must remain off unless intentionally turned on.               |  |

|         | P80      |              | General purpose input/output port. This function is enabled when external ready signal input is disabled.                                                                            |  |

|         | BGRNT    |              | Acknowledge output for external bus release. Outputs "L" when the external bus is released. The pin has this function when output is enabled.                                        |  |

| 165     | IN1      | D            | Input capture input pin. Since this input is used as required when selected as an input capture input, the port output must remain off unless intentionally turned on.               |  |

|         | P81      |              | General purpose input/output port. This function is enabled when external bus release acknowledge output is disabled.                                                                |  |

|         | BRQ      | D            | External bus release request input. Input "1" to request release of the external bus. The pin has this function when input is enabled.                                               |  |

| 166     | IN2      |              | Input capture input pin. Since this input is used as required when selected as an input capture input, the port output must remain off unless intentionally turned on.               |  |

|         | P82      |              | General purpose input/output port. The pin has this function when the external bus release request input is disabled.                                                                |  |

| 167     | RD       | D            | External bus read strobe output. It is available in the external bus mode.                                                                                                           |  |

| 107     | P83      |              | General purpose input/output port. This is enabled at single chip mode.                                                                                                              |  |

| 168     | WR0      | D            | External bus write strobe output. It is available in the external bus mode.                                                                                                          |  |

| 100     | P84      |              | General purpose input/output port. This is enabled at single chip mode.                                                                                                              |  |

|         | WR1      |              | External bus write strobe output. This function is enabled when $\overline{WR1}$ output is enabled in external bus mode.                                                             |  |

| 169     | IN3      | D            | Input capture input pin. Since this input is used as required when selected as an input capture input, the port output must remain off unless intentionally turned on.               |  |

|         | P85      |              | General purpose input/output port. The pin has this function when the external bus write-enable output is disabled.                                                                  |  |

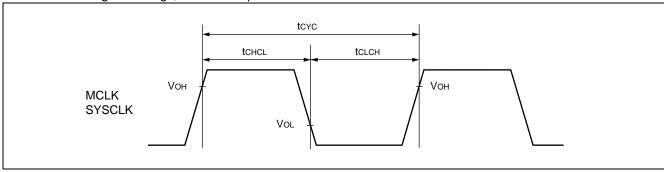

| 170     | SYSCLK   | С            | System clock output The pin has this function when system clock output is enabled. This outputs the same clock as the external bus operating frequency. (Output halts in stop mode.) |  |

|         | P90      |              | General purpose input/output port. The pin has this function when system clock output is disabled.                                                                                   |  |

| 171     | P91      | С            | General purpose input/output port.                                                                                                                                                   |  |

## (Continued)

| Pin no. | Pin name | Circuit type | Description                                                                                                                                                                                    |  |

|---------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 172     | MCLK     | С            | Memory clock output. This function is enabled when the memory clock output is enabled. This outputs the same clock as the external bus operating frequency. (Output halts in sleep/stop mode.) |  |

|         | P92      |              | General purpose input/output port. This function is enabled when the memory clock output is disabled.                                                                                          |  |

| 173     | P93      | С            | General purpose input/output port.                                                                                                                                                             |  |

| 174     | ĀS       | С            | Address strobe output. This function is enabled when address strobe output is enabled.                                                                                                         |  |

| 174     | P94      |              | General purpose input/output port. This function is enabled when address load output is disabled.                                                                                              |  |

## • Power supply and GND pins

| Pin no.                                         | Pin name  | Description                                                       |  |

|-------------------------------------------------|-----------|-------------------------------------------------------------------|--|

| 17, 35, 65, 79, 93, 96, 114, 136, 145, 162, 175 | Vss       | GND pins. Apply equal potential to all of the pins.               |  |

| 18, 36, 66, 80, 97, 115, 142, 146, 163, 176     | Vcc       | 3.3 V power supply pin. Apply equal potential to all of the pins. |  |

| 45                                              | DAvs      | GND pin for D/A converter                                         |  |

| 46                                              | DAvc      | Power supply pin for D/A converter                                |  |

| 62                                              | AVcc      | Analog power supply pin for A/D converter                         |  |

| 63                                              | AVRH      | Reference power supply pin for A/D converter                      |  |

| 64                                              | AVss/AVRL | Analog GND pin for A/D converter                                  |  |

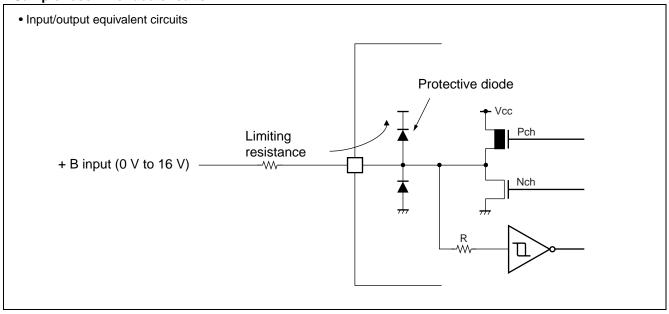

## ■ I/O CIRCUIT TYPE

| Туре | Circuit type                                                                    | Remarks                                                                                                                                                                                  |

|------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А    | Standby control                                                                 | Oscillation feedback resistance: approx. 1 MΩ                                                                                                                                            |

| В    | X1A  X0A  Standby control                                                       | Oscillation feedback resistance for low speed (subclock oscillation): approx. 7 MΩ                                                                                                       |

| С    | Pull-up control  Digital output  Digital output  Digital input  Standby control | CMOS level output CMOS level input  With standby control With Pull-up control Pull-up resistance = approx. 50 kΩ (Typ)  IoL = 8 mA                                                       |

| D    | Pull-up control  Digital output  Digital output  Digital input  Standby control | <ul> <li>CMOS level output</li> <li>CMOS level hysteresis input</li> <li>With standby control</li> <li>With Pull-up control</li> <li>Pull-up resistance = approx. 50 kΩ (Typ)</li> </ul> |

| Туре | Circuit type                          | Remarks                                                                                           |

|------|---------------------------------------|---------------------------------------------------------------------------------------------------|

|      | Digital output                        | CMOS level output     CMOS level hysteresis input                                                 |

| E    | Digital output  Digital input         | With stand voltage of 5 V  IoL = 4 mA                                                             |

|      |                                       |                                                                                                   |

|      | Digital output                        | <ul><li>Nch open drain output</li><li>CMOS level hysteresis input</li></ul>                       |

| F    | <del>,,,</del>                        | with standby control                                                                              |

|      | ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ ☐ | With stand voltage of 5 V                                                                         |

|      | Standby control                       | I <sub>OL</sub> = 15 mA                                                                           |

| G    | Analog input                          | Analog input with switch                                                                          |

| н    | Digital input                         | CMOS level hysteresis input                                                                       |

| I    | Digital input                         | • CMOS level hysteresis input $ \mbox{with pull-up resistor}                                    $ |

|      |                                       |                                                                                                   |

### **■ HANDLING DEVICES**

#### Preventing Latchup

Latch-up may occur in a CMOS IC if a voltage greater than VCC or less than VSS is applied to an input or output pin or if an above-rating voltage is applied between VCC and VSS. A latchup,if it occurs, significantly increases the power supply current and may cause thermal destruction of an element. When you use a CMOS IC, be very careful not to exceed the maximum rating.

#### • Treatment of Unused Input Pins

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, for example, using a pull-up or pull-down resistor.

#### · About power supply pins

In products with multiple  $V_{CC}$  or  $V_{SS}$  pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to an external power supply and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the Vcc and Vss pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between  $V_{CC}$  and  $V_{SS}$  near this device.

### · About Crystal oscillator circuit

Noise near the X0, X1, X0A and X1A pins may cause the device to malfunction. Design the circuit board so that X0, X1, X0A, X1A, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0, X1, X0A and X1A pins surrounded by ground plane because stable operation can be expected with such a layout.

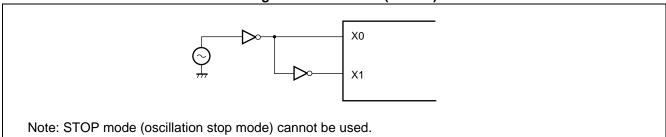

### • Notes on Using External Clock

When external clock is selected, supply it to X0 pin generally, and simultaneously the opposite phase clock to X0 must be supplied to X1 pin. However, in this case the stop mode(oscillator stop mode) must not be used. (This is because the X1 pin stops at High level output in STOP mode.)

#### Using an external clock (normal)

#### Clock control block

Take the oscillation stabilization wait time during Low level input to the INIT pin.

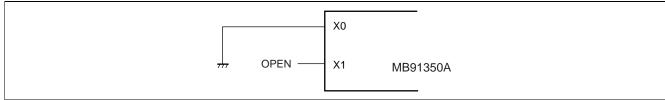

#### · Notes on not using the sub clock

When no oscillator is connected to the X0A and X1A pins, pull down the X0A pin and open the X1A pin.

#### • Treatment of NC and OPEN pins

Pins marked as NC and OPEN must be left open-circuit.

#### • Mode pins (MD0 to MD2)

These pins should be connected directly to Vcc or Vss.

To prevent the device erroneously switching to test mode due to noise, design the printed circuit board such that the distance between the mode pins and Vcc or Vss is as short as possible and the connection impedance is low.

#### Operation at start-up

The INIT pin must be at Low level when the power supply is turned on.

Immediately after the power supply is turned on, hold the Low level input to the  $\overline{\text{INIT}}$  pin for the settling time required for the oscillator circuit to take the oscillation stabilization wait time for the oscillator circuit. (For INIT via the  $\overline{\text{INIT}}$  pin, the oscillation stabilization wait time setting is initialized to the minimum value.)

#### About oscillation input at power on

When turning the power on, maintain clock input until the device is released from the oscillation stabilization wait state.

#### Caution on Operations during PLL Clock Mode

Even if the oscillator comes off or the clock input stops with the PLL clock selected for this microcontroller, the microcontroller may continue to operate at the free-running frequency of the PLL's internal self-oscillating oscillator circuit. Performance of this operation, however, cannot be guaranteed.

#### · External bus setting

This model guarantees an external bus frequency of 25 MHz.

Setting the base clock frequency to 50 MHz with DIVR1 (external bus base clock division setting register) initialized sets the external bus frequency also to 50 MHz. Before changing the base clock frequency, set the external bus frequency not exceeding 25 MHz.

### MCLK and SYSCLK

MCLK and SYSCLK has a difference that MCLK stops in SLEEP/STOP mode but SYSCLK stops only in STOP mode. Use either depending on each application.

Upon initialization, MCLK becomes invalid (PORT) and SYSCLK becomes valid. To use MCLK, set the port function register (PFR) to select the use of that clock.

#### • Pull-up control

Connecting a pull-up resistor to the pin serving as an external bus pin cannot a guarantee the "**ELECTRICAL** CHARACTERISTICS 4. AC Characteristics (4) Normal Bus Access Read/Write Operation, (5) Multiplex Bus Access Read/Write operation and (7) Hold Timing".

Even the port for which a pull-up resistor has been set is invalid in stop mode with HIZ = 1 or in hardware standby mode.

#### Sub clock select

Immediately after switching from main clock mode to subclock mode for the clock source, insert at least one NOP instruction.

```

(ldi #0x0b, r0)

(ldi #_CLKR, r12)

stb r0, @r12  // sub-clock mode

nop  // Must insert NOP instruction

```

#### • Bit Search Module

The BSD0, BSD1, and BDSC registers are accessed only in words.

#### D-bus memory

Do not allocate the code area in memory on the D-bus because no instruction fetch takes place to the D-bus. Executing an instruction fetch to the D-bus area causes wrong data to be interpreted as code, possibly letting the device to run out of control.

#### • Low Power Consumption Mode

To enter the sleep or stop mode, be sure to read the standby control register (STCR) immediately after writing to it. Precisely, use the following sequence.

Set the I flag, ILM, and ICR to, after returning from standby mode, branch to the interrupt handler having caused the device to return.

```

(ldi

#value_of_standby, r0)

(ldi

#_STCR, r12)

stb

r0. @r12

// set STOP/SLEEP bit

Idub

@r12, r0

// Must read STCR

// after reading, go into standby

@r12, r0

ldub

mode

// Must insert NOP *5

nop

nop

nop

nop

nop

```

#### • Switch shared port function

To switch between the use as a port and the use as a dedicated pin, use the port function register (PFR). Note, however, that bus pins are switched depending on external bus settings.

#### Pre-fetch

When accessing a prefetch-enabled little endian area, be sure to use word access (in 32-bit, word length) only. Byte or halfword access results in wrong data read.

## • I/O port access

Ports are accessed only in bytes.

#### • Built-in RAM

Immediately after a reset is canceled, the internal RAM allocation restricting function is still working, allowing only 4 KB to be used for data and for program execution irrespective of the on-chip RAM capacity.

#### FLASH MEMORY

In programming mode, flash memory cannot be used as an interrupt vector table. A reset is possible.

• Notes on the PS register

As the PS register is processed by some instructions in advance, exception handling below may cause the interrupt handling routine to break when the debugger is used or the display contents of flags in the PS register to be updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event, it performs operations before and after the EIT as specified in either case.

- 1. The following operations are performed when the instruction followed by a DIVOU/DIVOS instruction results in: (a) acceptance of a user interrupt or NMI, (b) single-stepping, or (c) a break at a data event or emulator menu.

- The D0 and D1 flags are updated in advance.

- An EIT handling routine (user interrupt, NMI, or emulator) is executed.

- Upon returning from the EIT, the DIVOU/DIVOS instruction is executed and the D0 and D1 flags are updated to the same values as in (1).

- 2. The following operations are performed when the ORCCR/STILM/MOVRi and PS instructions are executed.

- The PS register is updated in advance.

- An EIT handling routine (user interrupt, NMI, or emulator) is executed.

- Upon returning from the EIT, the above instructions are executed and the PS register is updated to the same value as in (1).

### [Note on debugger]

· Step execution of RETI command

If an interrupt occurs frequently during single-stepping, the corresponding interrupt handling routine is executed repeatedly. This will prevent the main routine and low-interrupt-level programs from being executed. (Whenever RETI is single-stepped when interrupts by the timebase timer have been enabled, for example, the timebase timer routine causes a break at the beginning.)

Disable the corresponding interrupt when the corresponding interrupt handling routine no longer needs debugging.

#### Break function

If the address at which to cause a hardware break (including a event break) is set to the address currently contained in the system stack pointer or in the area containing the stack pointer, the user program causes a break after execution of one instruction.

To prevent this, do not set (word) access to the area containing the address in the system stack pointer as the target of a hardware break (including an event break).

#### • Internal ROM area

Do not set an area of internal ROM as a DMAC transfer destination.

• Simultaneous occurrences of a software break (INTE instruction) and a user interrupt/NMI

When an INTE instruction and a user interrupt/NMI are accepted simultaneously, the emulator debugger reacts as follows.

The emulator debugger stops while indicating a location in the user program, which is not a user-specified breakpoint. (It stops with the beginning of the user interrupt/NMI handling routine indicated.)

The user program cannot be re-executed correctly.

To prevent this problem, follow the instructions below.

When a software break and a user interrupt/NMI occur simultaneously, the emulator debugger may react as follows.

- The debugger stops pointing to a location other than the programmed breakpoints.

- The halted program is not re-executed correctly.

If this symptom occurs, use a hardware break in place of a hardware break. When using a monitor debugger, do not set a break at the relevant location.

- A stack pointer placed in an area set for a DSU operand break can cause a malfunction. Do not apply a data event break to access to the area containing the address of a system stack pointer.

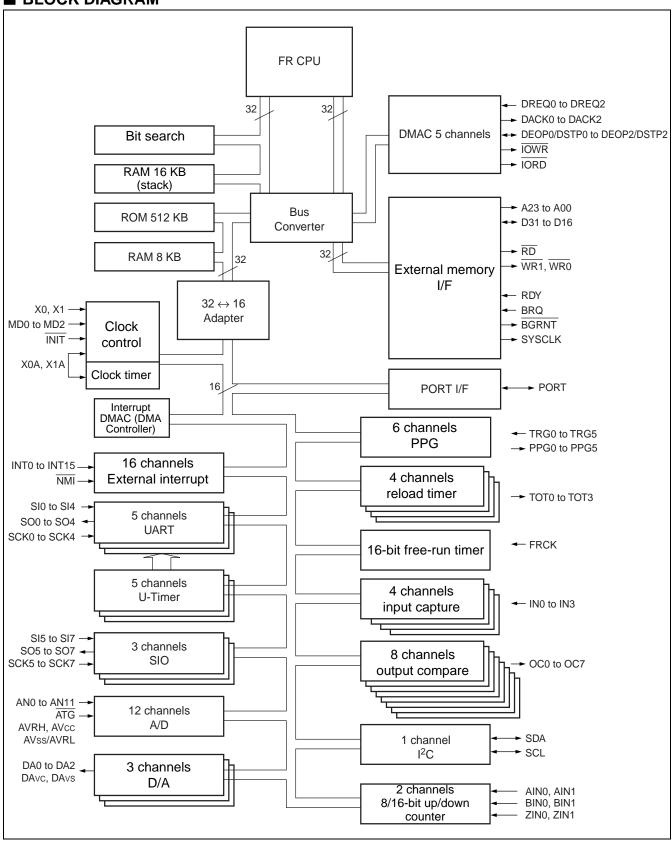

### **■ BLOCK DIAGRAM**

## **■ CPU AND CONTROL UNIT**

#### Internal architecture

The FR family CPU is a high performance core based on a RISC architecture while incorporating advanced instructions for embedded controller applications.

#### 1. Features

- RISC architecture employed. Basic instructions: Executed at 1 instruction per cycle

- General-purpose registers: 32-bit × 16 registers

- 4GB linear memory space

- Multiplier integrated.

- 32-bit x 32-bit multiplication: 5 cycles.

- 16-bit x 16-bit multiplication: 3 cycles

- Enhanced interrupt servicing.

- Fast response speed (6 cycles).

- Multiple interrupts supported.

- Level masking (16 levels)

- Enhanced I/O manipulation instructions.

- Memory-to-memory transfer instructions, Bit manipulation instructions

- High code efficiency. Basic instruction word length: 16-bit

- Low-power consumption. Sleep mode and stop mode

- Gear function

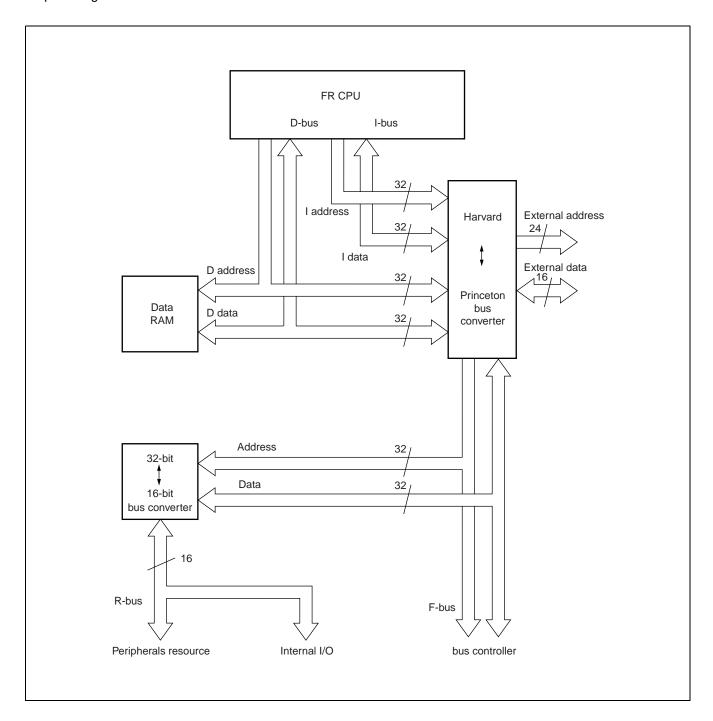

### 2. Internal architecture

The FR-family CPU has a Harvard architecture in which the instruction and data buses are separated.

The 32-bit/16-bit bus converter is connected to a 32-bit bus (F-bus), providing an interface between the CPU and peripheral resources. The Harvard-Princeton bus converter is connected to both of the I-bus and D-bus, providing an interface between the CPU and the bus controller.

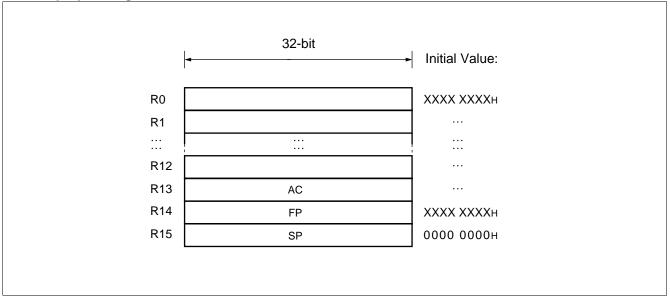

## 3. Programming model

Basic programming model 32-bit Initial Value: XXXX XXXXH R0 R1 **GENERAL** R12 ... PURPOSE **REGISTERS** R13 AC R14 FΡ XXXX XXXXH R15 SP 0000 0000н Program counter PC program status PS ILM SCR CCR Table base register TBR Return pointer RP System stack pointer SSP User stack pointer USP Multiplication and division MDH result register MDL

## 4. Register

General purpose registers

Registers R0 to R15 are general-purpose registers. The registers are used as the accumulator and memory access pointers for CPU operations.

Of these 16 registers, the registers listed below are intended for special applications, for which some instructions are enhanced.

R13: Virtual accumulator

R14 : frame pointer R15 : Stack pointer

The initial values of R0 to R14 after a reset are indeterminate. R15 is initialized to 0000 0000<sub>H</sub> (SSP value).

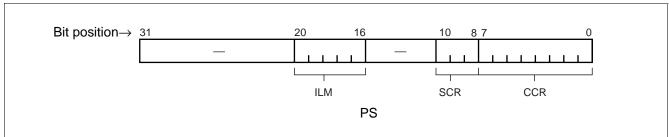

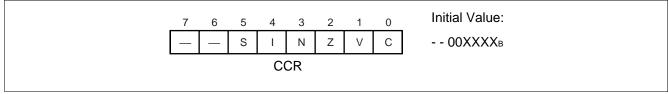

#### • PS (Program Status)

This register holds the program status and is divided into the ILM, SCR, and CCR.

The undefined bits in the following illustration are all reserved bits. Reading these bits always returns "0". Writing to them has no effect.

## • CCR (Condition Code Register)

S: Stack flag. Cleared to "0" by a reset.

I : Interrupt enable flag. Cleared to "0" by a reset.

N : Negative flag. The initial value after a reset is indeterminate.

Z : Zero flag. The initial value after a reset is indeterminate.

V : Overflow flag. The initial value after a reset is indeterminate.

C : Carry flag. The initial value after a reset is indeterminate.

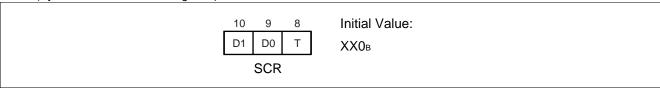

### • SCR (System Condition code Register)

Flag for step dividing

Stores intermediate data for stepwise multiplication operations.

Step trace trap flag

A flag specifying whether the step trace trap function is enabled or not.

Emulator use step trace trap function. The function cannot be used by the user program when using the emulator.

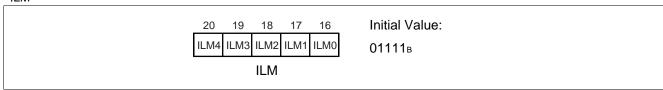

#### • ILM

This register stores the interrupt level mask value. The value in the ILM register is used as the level mask. Initialized to "15" (01111<sub>B</sub>) by a reset.

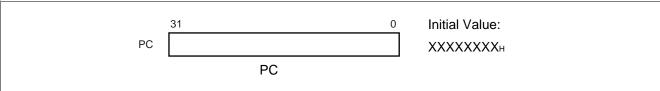

## • PC (Program Counter)

The program counter contains the address of the instruction currently being executed.

The initial value after a reset is indeterminate.

| TDD /Toble Doce Decistor)                              |                                 |                 |                                                             |

|--------------------------------------------------------|---------------------------------|-----------------|-------------------------------------------------------------|

| • TBR (Table Base Register)                            |                                 |                 |                                                             |

|                                                        | 31                              | 0               | Initial Value:                                              |

| TBR                                                    |                                 |                 | 000FFC00н                                                   |

|                                                        | TBR                             |                 |                                                             |

| The table base register of the initial value after a r |                                 | he vector table | e used for servicing EIT events.                            |

| RP (Return Pointer)                                    |                                 |                 |                                                             |

|                                                        | 31                              | 0               | Initial Value:                                              |

| RP                                                     |                                 |                 | XXXXXXXH                                                    |

|                                                        | RP                              |                 |                                                             |

| SSP (System Stack Pointer)                             |                                 |                 |                                                             |

|                                                        | 31                              | 0               | Initial Value:                                              |

| SSP                                                    |                                 |                 | 0000000н                                                    |

|                                                        | SSP                             |                 |                                                             |

| The SSP can be explicit                                | the stack pointer that specific |                 | e S flag is "0".<br>r saving the PS and PC when an EIT even |

| USP (User Stack Pointer)                               |                                 |                 |                                                             |

|                                                        | 31                              | 0               | Initial Value:                                              |

| USP                                                    |                                 |                 | XXXXXXXH                                                    |

|                                                        | USP                             |                 |                                                             |

The USP is the user stack pointer and functions as R15 when the S flag is "1".

The SSP can be explicitly specified.

The initial value after a reset is indeterminate.

This pointer cannot be used by the RETI instruction.

| Multiply & Divide registers |                                           |  |

|-----------------------------|-------------------------------------------|--|

|                             |                                           |  |

|                             | 31 0                                      |  |

| MDH                         |                                           |  |

| MDL                         |                                           |  |

| Mu                          | Itiplication and division result register |  |

These registers hold the results of a multiplication or division. Each of them is 32-bit long. The initial value after a reset is indeterminate.

### **■ MODE SETTINGS**

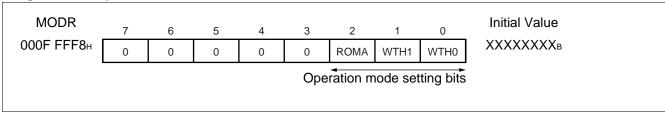

The FR family uses mode pins (MD2 to MD0) and a mode register (MODR) to set the operation mode.

#### 1. Mode Pins

The MD2, MD1, and MD0 pins specify how the mode vector fetch is performed.

| N   | lode Pi | ns  | Mode name                | Reset vector | Remarks                                          |  |

|-----|---------|-----|--------------------------|--------------|--------------------------------------------------|--|

| MD2 | MD1     | MD0 |                          | access area  | Remarks                                          |  |

| 0   | 0       | 0   | Internal ROM mode vector | Internal     |                                                  |  |